A CONVENIENT MULTIPLEXING SCHEME FOR ADDRESSING SMALL LIQUID CRYSTAL MATRIX DISPLAYS

N.V. Madhusudana and T.N. Ruckmongathan Raman Research Institute, Bangalore 560 080, India

In this paper, a convenient method for multiplexing small liquid crystal matrix displays is presented. For a matrix of N rows, the method consists of addressing the rows with all possible combinations of a binary voltage scheme. For each of these 2<sup>N</sup> combinations, a proper binary voltage is selected for each of the columns to get a majority-advantage compared to the picture pattern to be displayed. A mathematical analysis of this scheme is given. Though the contrast ratio with the present scheme is slightly less than that obtained with the conventional scheme it has the advantage of having a very large duty factor and of requiring only one power supply. The simplicity of the scheme is exploited to construct and operate a 16-segment alphanumeric display panel.

### INTRODUCTION

For many low cost, high volume type of applications, it would be useful to have relatively cheap, multiplexed alphanumeric liquid crystal displays (LCDs). We have tried to develop such a display with simple circuitry.

#### THE MULTIPLEXING SCHEME

From the practical point of view, it is an extremely simple matter to generate a sequence of binary numbers using a counter. We have made use of this facility in developing an addressing scheme suitable for LCDs.

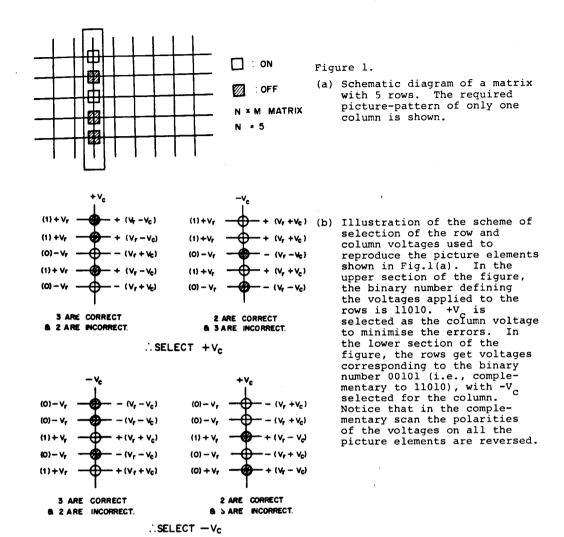

Consider a matrix with N rows. For reasons which will be obvious soon, let N be an odd number. If, as usual, 1 stands for 'high' and 0 for 'low' voltages (positive logic) a total of 2<sup>N</sup> different signals (which are the possible N-bit binary numbers) can be applied to the N rows. With each of these possible voltage-patterns on the rows, we will apply such a voltage to a given column that the error with reference to the required pattern is minimised. This is illustrated in Fig.l for a matrix with 5 rows. In general, if '1' is  $+V_r$  and '0' is  $-V_r$  on the rows, we can apply either  $+V_c$  or  $-V_c$  to the columns. Only the RMS voltage is relevant to the electro-optic response of the LCD and at any given time the squared voltage on any given element is  $(v_r + v_c)^2$  or  $(v_r - v_c)^2$ . It is not necessary to consider all the  $2^N$  possible binary numbers applied to the rows, since one half of them will be complementary to the other half (see fig.l). Let us assume that a given element in a given column should be 'ON'. The RMS voltage on that element can be calculated as follows: Let P be the number of times that the element has a squared voltage equal to  $(v_r + v_c)^2$ . In the remaining number of scans, viz.,

Proceedings of the International Liquid Crystals Conference, Bangalore, 1979. Ed. S Chandrasekhar. Heyden 1980

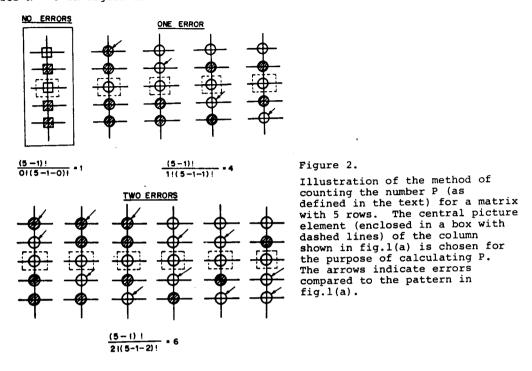

$(2^{N-1}-P)$  scans, that element will have a squared voltage equal to  $(v_r-v_c)^2$ . Only once during the  $2^{N-1}$  scans, all the elements of the given column will have the correct voltages (i.e., 'ON' elements have  $(v_r+v_c)^2$  and 'OFF' elements have  $(v_r-v_c)^2$ ). There will be one mistake in N out of the  $2^{N-1}$  scans. However, we want the given element to be 'ON'. So, in (N-1) scans the given element is 'ON' when the picture-pattern in the given column has one mistake. This can also be written as (N-1)!/1!(N-2)! which is the number of ways of selecting one out of (N-1) elements of the column.

In a similar manner, when there are two mistakes in the picture-pattern, excluding the cases where the given element has a mistake, the number of times it is 'ON' is (N-1)!/2!(N-3)!.

We can continue this series till we reach the maximum possible error. By choice, this error cannot exceed (N-1)/2. The counting procedure is illustrated for N=5 in figure 2.

Hence the total number of scans for which an 'ON' element has  $(v_r + v_c)^2$  as the squared voltage is given by

$$P = \frac{\frac{N-1}{2}}{\sum_{m=0}^{N-1} \frac{(N-1)!}{m! (N-1-m)!}}$$

(1)

In the remaining  $(2^{N-1}-P)$  scans, the element has  $(v_r-v_c)^2$  as the squared voltage. Hence the RMS voltage on the 'ON' element is

$$V_{ON}(RMS) = \left[ \frac{P(V_r + V_c)^2 + (2^{N-1} - P)(V_r - V_c)^2}{2^{N-1}} \right]^{\frac{1}{2}}$$

(2)

In a similar manner,

$$V_{OFF}(RMS) = \left[ \frac{P(V_r - V_c)^2 + (2^{N-1} - P)(V_r + V_c)^2}{2^{N-1}} \right]^{\frac{1}{2}}$$

(3)

It can be easily shown that  $V_{ON}/V_{OFF}$  is optimised for  $V_r = V_c$ . Then

$$V_{ON}/V_{OFF} = \sqrt{P/(2^{N-1}-P)}$$

(4)

Let  $V_r = V_c = V$ . In fact we can chose '1' to be 'V' and '0' to be zero itself. Thus a single source of voltage is adequate to address the display. Further, when we scan through the complementary  $2^{N-1}$  binary numbers, any given element will get an equal number of voltage pulses of opposite sign, so that a DC-free operation is automatically ensured (see also fig.1).

When N is even, it is clear that the choice of the voltage to be applied to the column electrode becomes ambiguous when N/2 mistakes occur for a given voltage-pattern on the row-electrodes. Covering both the possibilities is equivalent to scanning a matrix with (N+1) rows, i.e., eqn.(4) holds good with N replaced by N+1.

It is also clear that since a total of  $2^{N}$  scans are needed to cover all possibilities, the number of scans rapidly increases with N. Hence this method of addressing is useful only for small matrices.

The optical contrast ratio depends on the RMS value of  $(V_{ON}/V_{OFF})$ . It is listed below for a few values of N and compared with the values for the conventional scanning method due to Alt and Pleshko (1).

|   |   | RMS | value of          | (V <sub>ON</sub> /V <sub>OE</sub> | <sub>F</sub> ) |

|---|---|-----|-------------------|-----------------------------------|----------------|

|   |   |     | Present<br>method | Alt and<br>Pleshko                |                |

|   |   |     | R <sub>p</sub>    | R <sub>AP</sub>                   | RAP/RP         |

| N | = | 3   | 1.732             | 1.932                             | 1.115          |

| N | = | 5   | 1.483             | 1.618                             | 1.091          |

| N | = | 7   | 1.382             | 1.488                             | 1.077          |

| N | = | 9   | 1.324             | 1.414                             | 1.068          |

Hence the Alt and Pleshko values are always higher than the ones got by the present method. However, as N increases the two values approach each other.

Nontheless, in view of the advantages of the new method, viz., (a) need for a <u>single</u> voltage source, and (b) DC-free operation, we have used it in addressing a 16-segment

alphanumeric display. An additional advantage is that since, in the present method, an ON element is 'ON' most of the time (i.e., it has a relatively 'large' duty factor) a flicker-free operation is ensured even with relatively low scanning rates. (This may be compared with the duty factor of 1/N in the conventional method).

We very recently came across a paper by Clark et al (2) in which they appear to have considered a similar multiplexing technique. By using the results of a computer simulation analysis, they have conjectured that

$$V_{ON}/V_{OFF} = \left[1 + \left(\frac{2^{2q-1}}{\binom{2q}{q}} - \frac{1}{2}\right)^{-1}\right]^{\frac{1}{2}}$$

(5)

where q is an integer, N=2q+1 and  $\binom{2q}{q}$  denotes a binominal coefficient. By using binominal series, it can be easily shown that (4) reduces to (5). Thus our mathematical analysis confirms the conjecture by Clark et al.

### 16-SEGMENT ALPHANUMERIC DISPLAY

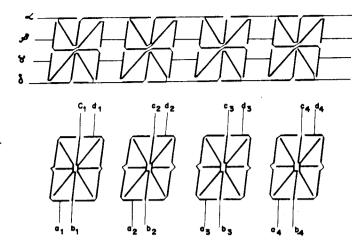

We treat each character as a  $4 \times 4$  matrix. The interconnections on the top and bottom plates are shown in figure 3.

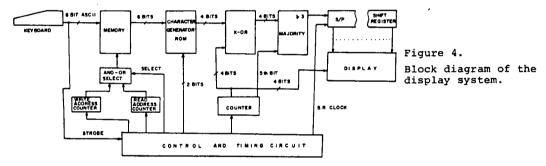

Since we did not have a standard character generator IC for addressing such a display, a 1702EPROM was programmed to convert the ASCII code from a key board

b

Photographs of two alpha-numeric patterns of a TN display panel with (a) parallel polarizers and (b) perpendicular polarizers. Figure 5

Figure 3.

The electrode patterns and the interconnections on the top and bottom plates of the display panel.

to the code necessary to address this display. The total memory required for 64 characters is  $64 \times 4 \times 4 = 1024$  in the organisation  $256 \times 4$ . The block diagram of the system is given in figure 4. The logic circuitry required to produce the data for columns is simple and consists only of finding the number of coincidences of the column data with the addressing waveform and making a simple majority decision.

Photographs of some preliminary twisted nematic displays constructed on the basis of this scheme are shown in figure 5. We feel that if the display performance is optimized by a suitable choice of materials, this will be a convenient method of addressing the displays.

## ACKNOWLEDGEMENT

We are indebted to Prof. S. Chandrasekhar for several useful discussions. Our thanks are also due to Mr. K. Subramanya and to Mr. H. Subramonyam for help in constructing the displays. This work was partially supported by the Indian Space Research Organization.

# REFERENCES

- 1. P.M. Alt and P. Pleshko, IEEE Trans. ED-21, 146 (1974).

- 2. K.G. Clark, I.A. Shanks and N.J. Patterson, SID Digest, p.110 (1979).